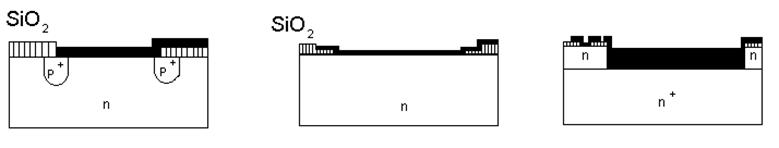

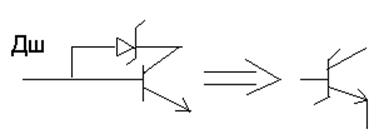

Диоды шоттки

Активные элементы для быстродействующих и сверхскоростных ИС.

Диоды Шоттки.

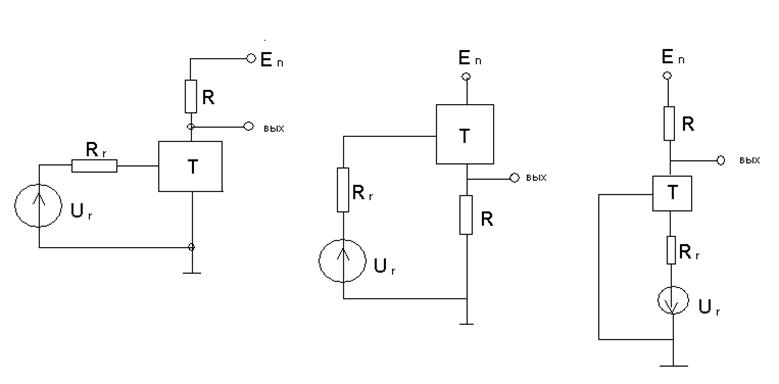

а) б) в)

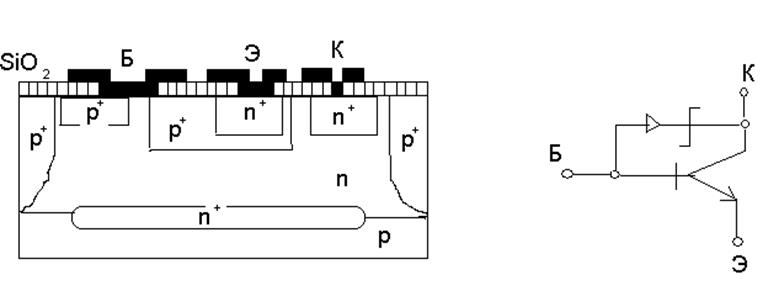

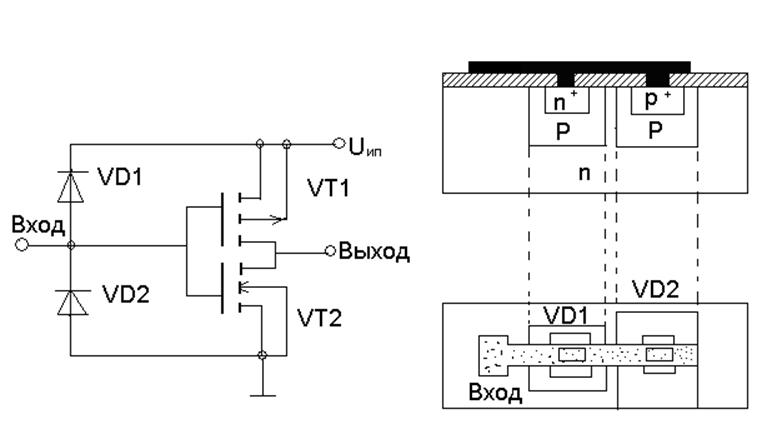

Транзисторы с диодами Шоттки.

Расчет и проектирование диодов

,

,

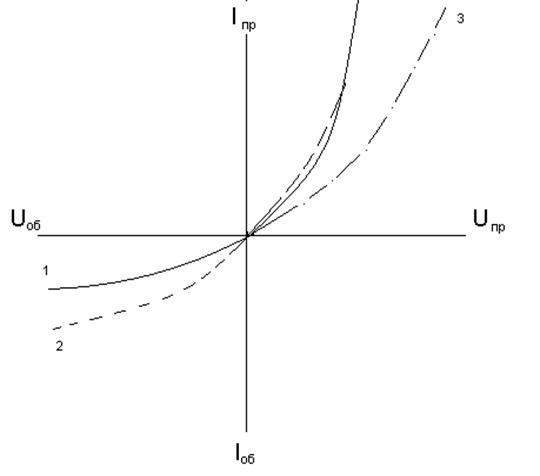

ВАХ диода представлена кривой 1 на рис.

>>1,

>>1,

, где

, где

![]() и

и ![]() . Емкость Сб связано с накоплением зарядов вблизи перехода, а

. Емкость Сб связано с накоплением зарядов вблизи перехода, а ![]() — с накоплением в областях, удаленных от перехода

— с накоплением в областях, удаленных от перехода

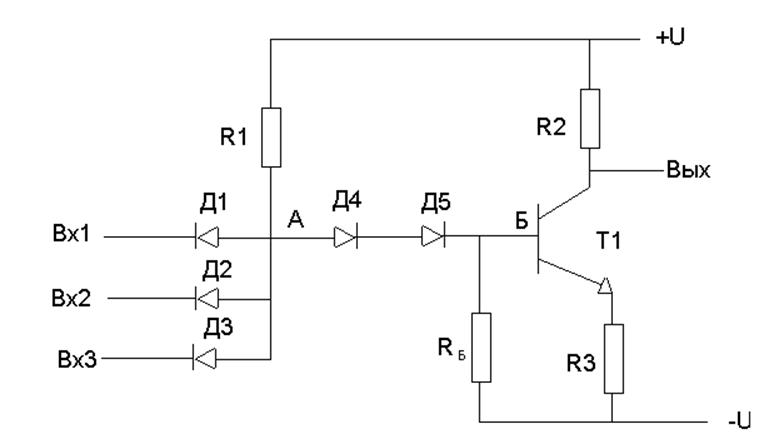

ДТЛ – схемы.

Рис. Схема ДТЛ.

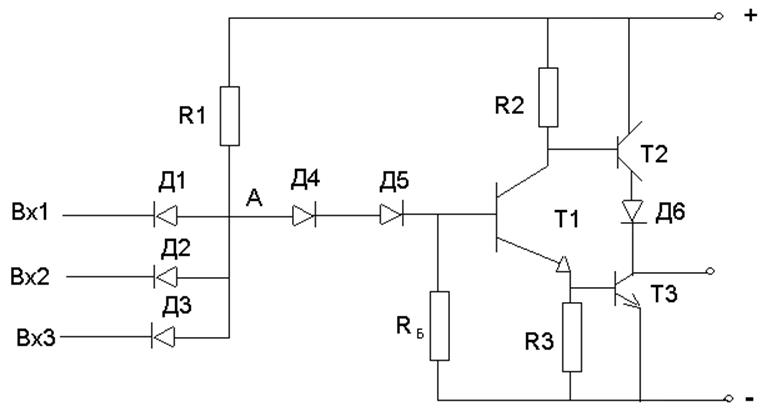

Рис. Схема ДТЛ со сложным инвертором.

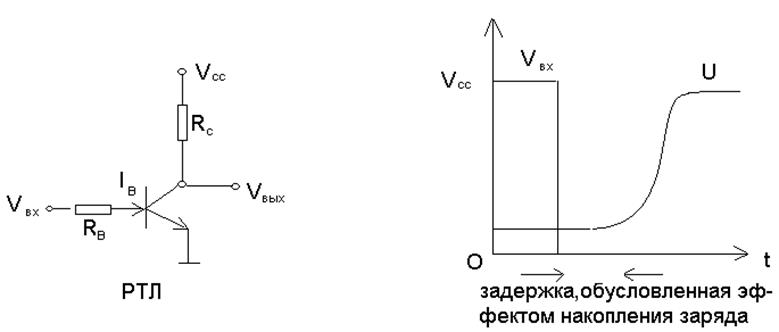

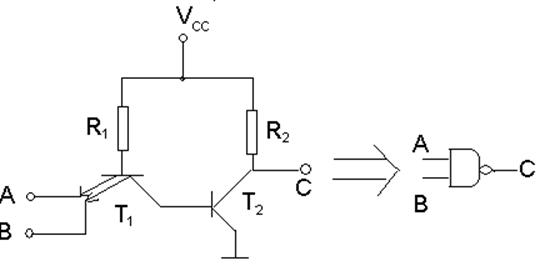

Базовые логические схемы на биполярных транзисторах

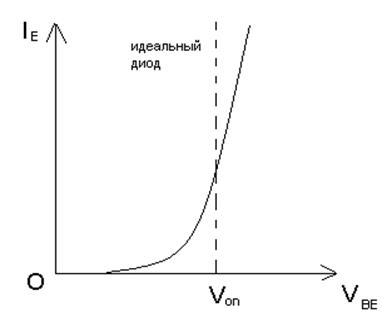

Рис. Характеристики IE-VBE для ненасыщенного режима.

ТТЛ-схемы.

Двухвходовой вентиль И-НЕ с многоэмиттерным транзистором приведен на рис.

а)А=0; б)А=В=1; в)А=1; В=0;

![]()

падении напряжение на

падении напряжение на ![]() переходе;

переходе; ![]() паразитное сопротивление базы Т1 ;

паразитное сопротивление базы Т1 ;  ,

,  транзисторов Т1, Т2 считаются равными.

транзисторов Т1, Т2 считаются равными. ![]() — ку. потоку для обратного направления в Т1

— ку. потоку для обратного направления в Т1

Если же (в) один из входов имеет потенциал источника питания, а второй соединен с «землей», то токи ![]() и

и ![]() определяются как

определяются как

;

;  ,

,

, коэффициент усиления по току паразитного горизонтального

, коэффициент усиления по току паразитного горизонтального  транзистора, образованного двумя эмиттерными переходами и базой.

транзистора, образованного двумя эмиттерными переходами и базой.

. Если в рис. (а)

а) б)

транзистор Т2 закрыт, то в схеме от источника питания ![]() через

через ![]() проходит ток

проходит ток ![]() и напряжение

и напряжение  . Если транзистор Т2 открыт (рис. б), то через него проходит ток

. Если транзистор Т2 открыт (рис. б), то через него проходит ток  и напряжение

и напряжение

. Для того чтобы работал Т2 в области насыщения, необходимо, чтобы ток

. Для того чтобы работал Т2 в области насыщения, необходимо, чтобы ток  превышал ток коллектора Т2, где

превышал ток коллектора Т2, где ![]() — ток базы Т2 и выполнялось условие

— ток базы Т2 и выполнялось условие

>

> , где

, где ![]() — к. у. по току Т2; m – число эмиттеров в транзисторе первого каскада ( коэффициент объединения по входу)

— к. у. по току Т2; m – число эмиттеров в транзисторе первого каскада ( коэффициент объединения по входу)

Потребляемая мощность

на выходе

на выходе

Среднее значение потребляемой мощности  .

.

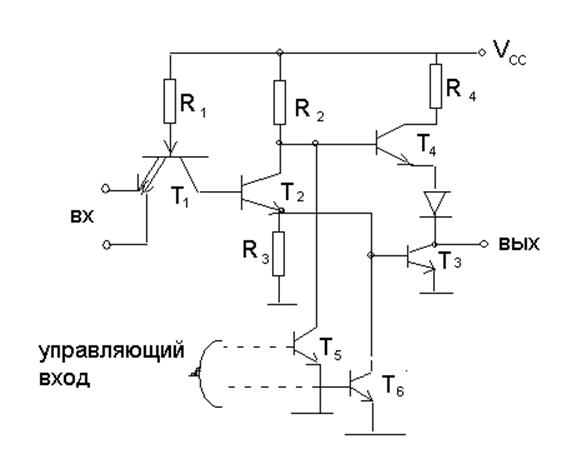

На базе ТТЛ-схем могут быть реализованы устройства с тремя состояниями (рис. )![]()

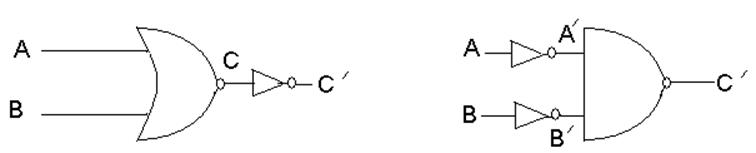

ТТЛШ – схемы.

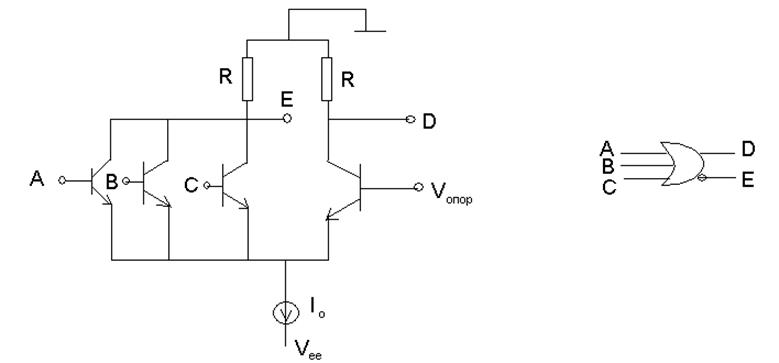

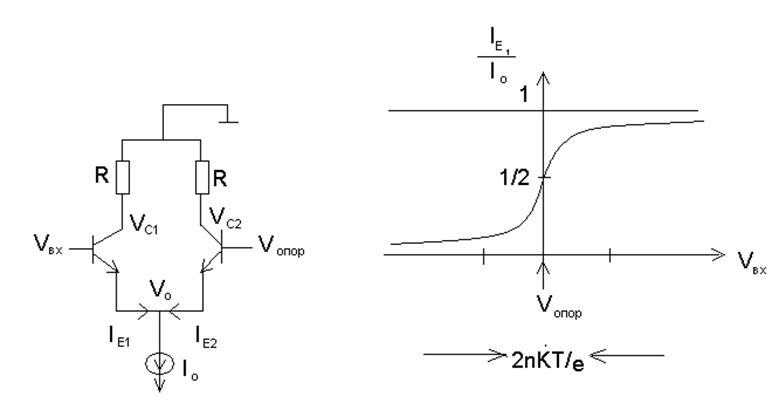

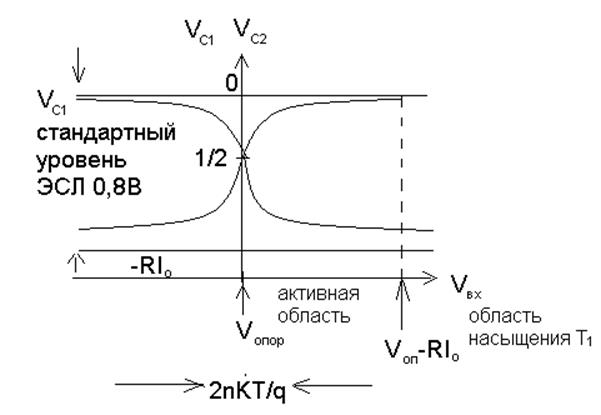

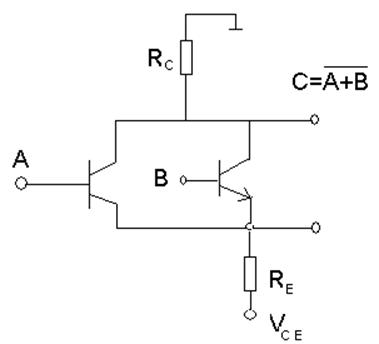

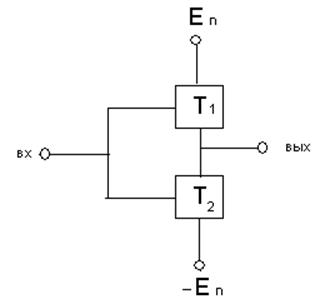

ЭСЛ-схемы.

D=A+B+C

E=

Распределение токов в ЭСЛ – схеме

Откуда  ;

;

;

;  ;

;

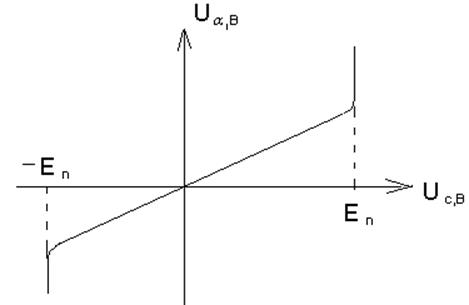

Уравнение графически можно представить (рис.)

Непороговые логические схемы

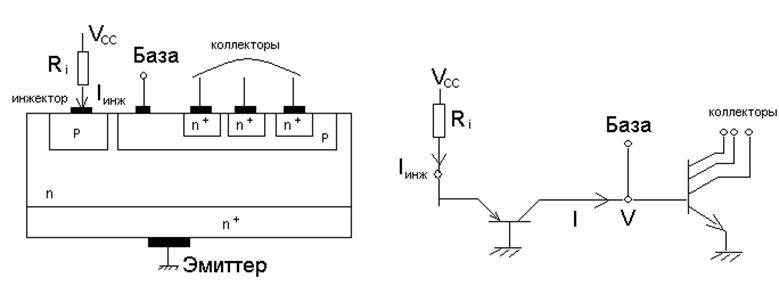

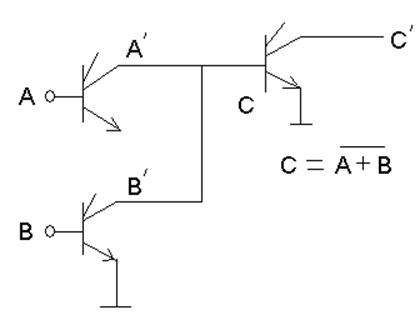

И2Л – схемы.

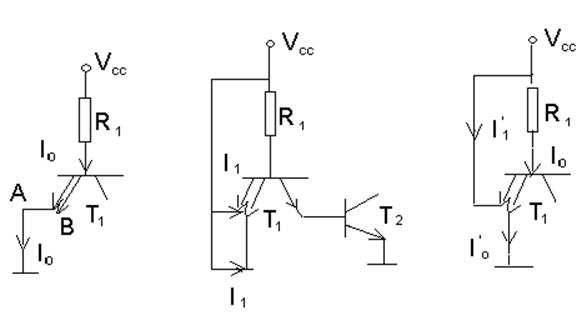

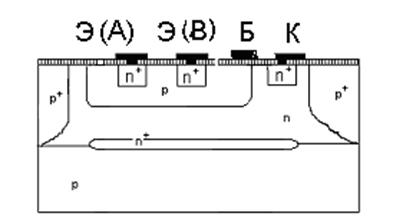

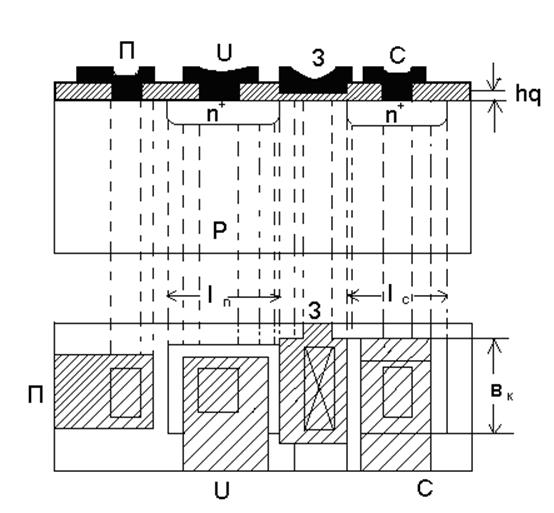

На рис. представлены И2Л – структура и ее эквивалентная схема:

для коллекторного тока можно получить следующее выражение :

(А)

(А)

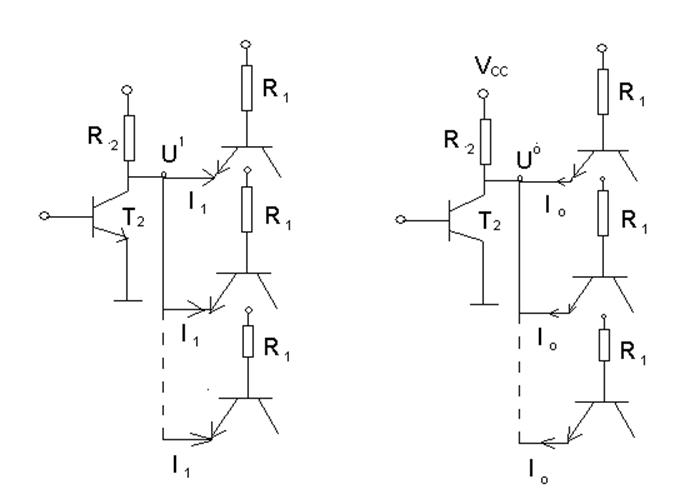

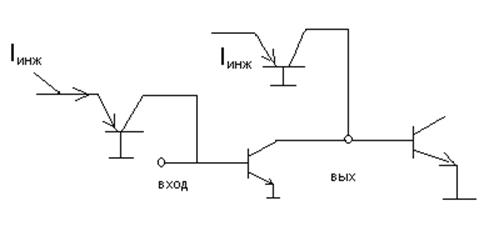

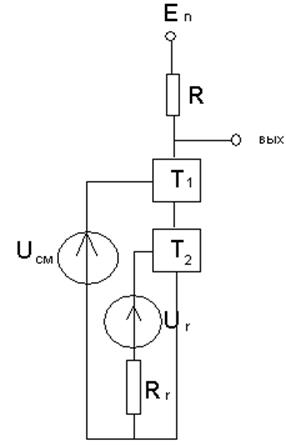

На рис. показана схема инвертора, полученного путем последовательного соединения двух И2Л – схем.

Вспомогательные элементы микросхем

Фигуры совмещения

Ключ –

Тестовые элементы —

Параметры логических интегральных микросхем. К параметрам логических ИМС относятся:

1)входное и выходное напряжения логической единицы ![]() и

и  — значения высокого уровня напряжения на входе и выходе микросхемы;

— значения высокого уровня напряжения на входе и выходе микросхемы;

2)входной ![]() и выходной

и выходной ![]() токи логической единицы, входной

токи логической единицы, входной ![]() и выходной

и выходной ![]() токи логического нуля;

токи логического нуля;

3)входное и выходное напряжение логического нуля![]() и

и

4)логический перепад сигнала  , пороговое напряжение

, пороговое напряжение

5)входное сопротивление логической ИМС – (различают  и

и  );

);

6)статическая помехоустойчивость

7)средняя потребляемая мощность  ,

,

8)коэффициент объединения по входу ![]()

9)коэффициент разветвления по выходу Кразв,

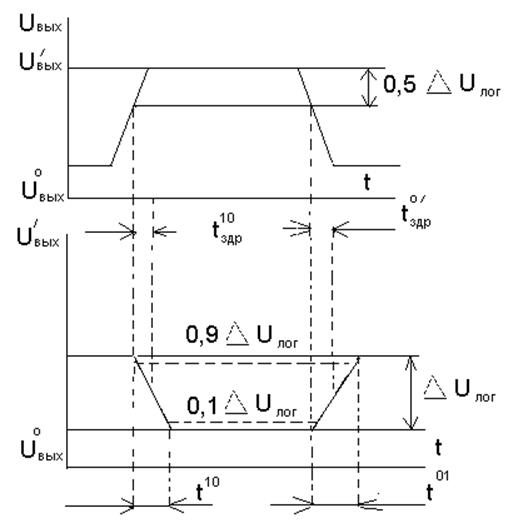

Динамические параметры логических ИМС можно проиллюстрировать с помощью временных диаграмм входного и выходного напряжения при переключении микросхемы (рис.)

![]() — время перехода из состояния логического нуля в состояние логической единицы, измеренное между уровнями 0,1 и 0,9 логического перепада сигнала;

— время перехода из состояния логического нуля в состояние логической единицы, измеренное между уровнями 0,1 и 0,9 логического перепада сигнала;

![]() — время задержки распространения сигнала при выключении микросхемы,

— время задержки распространения сигнала при выключении микросхемы,

![]() — время перехода из состояния логической единицы в состояние логического нуля, измеренное между уровнями 0,9 и 0,1 логического перепада сигнала;

— время перехода из состояния логической единицы в состояние логического нуля, измеренное между уровнями 0,9 и 0,1 логического перепада сигнала;

![]() — время задержки распространения сигнала при включении микросхемы,

— время задержки распространения сигнала при включении микросхемы,

.

.

Аналоговые ИС

Характеристики аналоговых ИМС

Для характеристики усилительных свойств используют коэффициенты усиления по напряжению  по току

по току  или по мощности

или по мощности  .

.

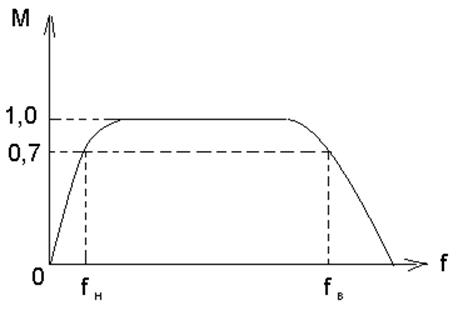

На рис. приведена нормированная АЧХ ![]() ;

; ![]() — номинальный КУ,

— номинальный КУ,

где

где  амплитуды высших гармоник

амплитуды высших гармоник

Элементы аналоговых ИМС

1) 2) 3)

Выходные каскоды должны, строится таким образом, чтобы обеспечить высокое значение выходной мощности. Большой мощности в нагрузке можно достичь в двухтактном каскаде (рис. ).

Дифференциальные каскоды. Эквивалентная схема дифференциального усилителя (ДУ) приведена на рис.

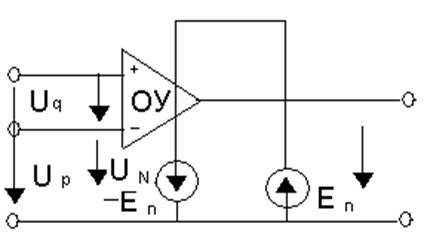

Операционные усилители (ОУ).

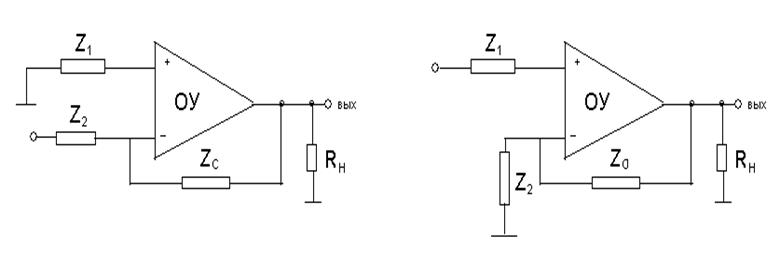

Схема цепей ОС в ОУ

Инвертирующая Неинвертирующая

Передаточная характеристика инвертирующего ОУ определяется выражением

,

,

для неинвертирующего

Коэффициент усиления синфазного сигнала :  .

.

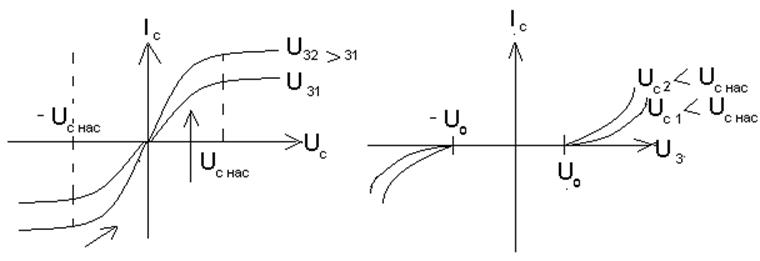

Зависимость выходного напряжения от напряжения синфазного сигнала приведена на рис.

Конструкции элементов полупроводниковых микросхем

на МДП – транзисторах

Принципы работы и классификация МДП-транзисторов.

Со встроенным каналом ![]() -типа с индуцированным каналом

-типа с индуцированным каналом

Вспомогательные элементы МДП-микросхем.

Охранные диоды

Охранные кольца.

Основные характеристики МДП-транзисторов

и их связь с конструктивно- технологическими параметрами

Основными для МДП-транзисторов являются стоковая характеристика  при

при  и стоко-затворная характеристика

и стоко-затворная характеристика  ) при

) при  .

.

Основные электрические параметры МДП-транзисторов: пороговое напряжение ![]() , крутизна

, крутизна ![]() , удельная крутизна

, удельная крутизна ![]() , дифференциальное сопротивление канала

, дифференциальное сопротивление канала ![]() , постоянная времени канала

, постоянная времени канала ![]() , входное сопротивление

, входное сопротивление ![]() .

.

. Сопротивление канала зависит и от величины ![]() и

и ![]() , которые при заданном напряжении на затворе влияют на концентрацию носителей в канале.

, которые при заданном напряжении на затворе влияют на концентрацию носителей в канале.

(1)

(1)

удельная емкость затвора относительно канала.

удельная емкость затвора относительно канала. ![]() — удельная крутизна.

— удельная крутизна.

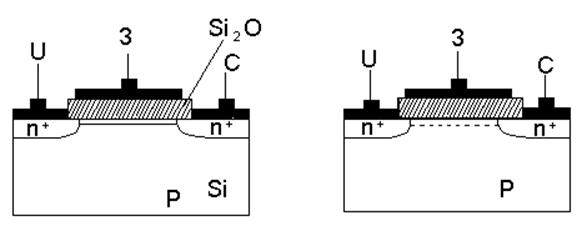

Конструкции МДП-транзисторов

с алюминиевой металлизацией

Конструкции МДП-транзисторов с ![]() затвором.

затвором.

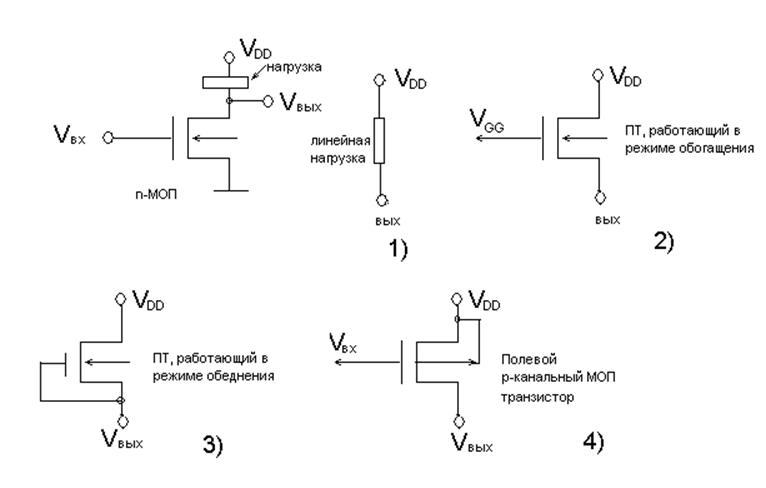

Основной тип МОП-инверторов. Базовая схема основного МОП – инвертора представлена на рис. совместно с этой схемой используют следующие нагрузки.

1,2,3 – пассивная нагрузка, 4 –активная нагрузка.

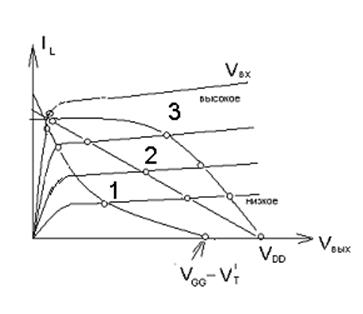

На рис. приведены характеристики переключательных элементов и характеристики пассивных нагрузочных элементов (по постоянному току). 1-нагрузка – полевой транзистор в режиме обогащения, 2 – нагрузка в виде резистора, 3 – нагрузка – полевой транзистор в режиме обеднения.

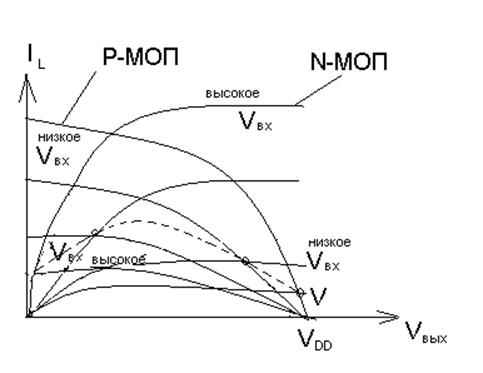

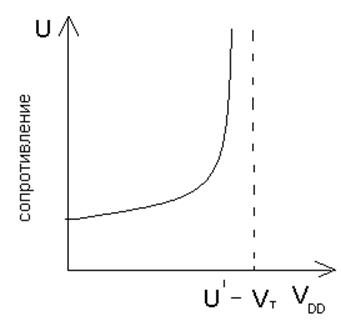

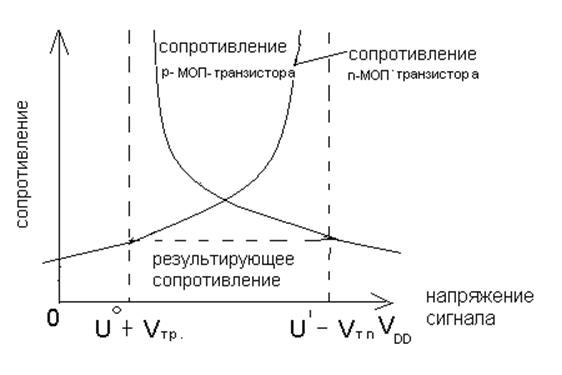

На рис. представлены характеристики (по постоянному току) активных нагрузочных элементов (![]() канальных МОП транзисторов) и переключательных

канальных МОП транзисторов) и переключательных ![]() МОП транзисторов. Перемещение рабочей точки пересечения обеих характеристик происходит по кривой, показанной пунктиром.

МОП транзисторов. Перемещение рабочей точки пересечения обеих характеристик происходит по кривой, показанной пунктиром.

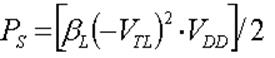

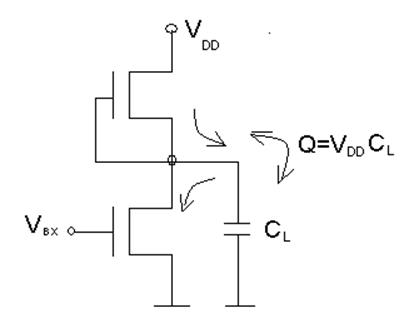

Потребляемая мощность МОП-инвертора.

В случае МОП-транзисторов, работающих в режимах обогащения/обеднения, ток при закрытом транзисторе практически равен нулю, и статической потребляемой мощностью в транзисторе можно пренебречь. Если транзистор открыт, то через него начинает проходить ток

,

, ![]() — пороговое

— пороговое ![]() — нижнего транзистора, где

— нижнего транзистора, где ![]() — коэффициент усиления полевого МОП транзистора и обычная потребляемая мощность составит

— коэффициент усиления полевого МОП транзистора и обычная потребляемая мощность составит

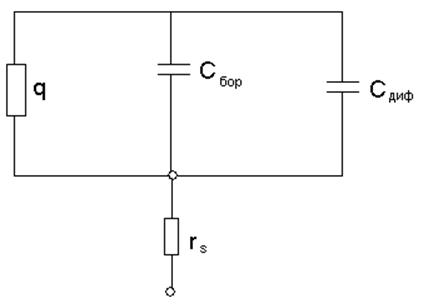

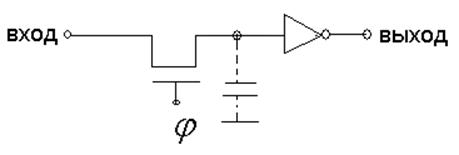

Аппроксимировав статические емкости двух полевых МОП-транзисторов, соединительных проводников и входа следующего каскада посредством конденсатора ![]() , как показано на рис. , можно рассчитать, что на одном

, как показано на рис. , можно рассчитать, что на одном

цикле зарядки потребляемая мощности, равная  , откуда динамическое потребление мощности можно определить как

, откуда динамическое потребление мощности можно определить как  , где

, где ![]() — средняя частота переключения.

— средняя частота переключения.

Итак, на один инвертор, выполненный на МОП транзисторах, работающих в режимах обогащения/обеднения, средняя потребляемая мощность составляет:

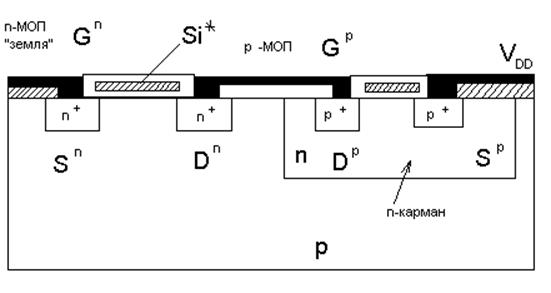

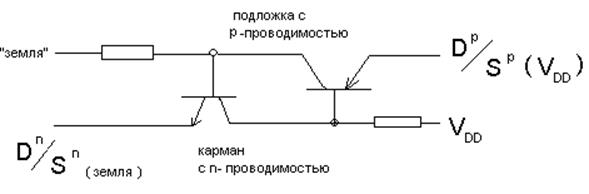

Тиристорный эффект «защелкивания» КМОП-структуры.

На рисунке в разрезе показан КМОП – инвертор. Сток нагрузочного ![]() канального МОП – транзистора и сток активного

канального МОП – транзистора и сток активного ![]() канального МОП-транзистора соединены металлическим проводником.

канального МОП-транзистора соединены металлическим проводником.

в инверторе формируется паразитная структура вида ![]() , показанная на рис.

, показанная на рис.

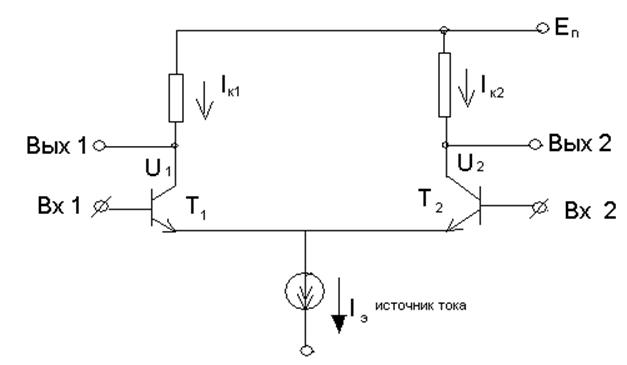

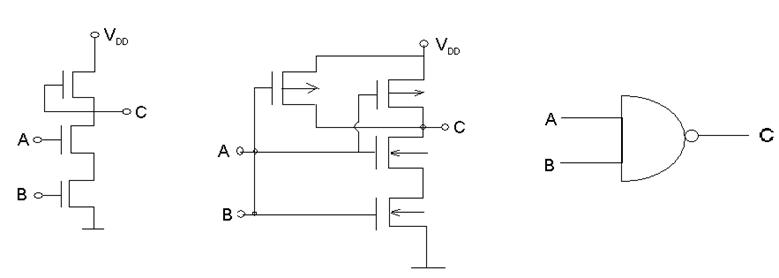

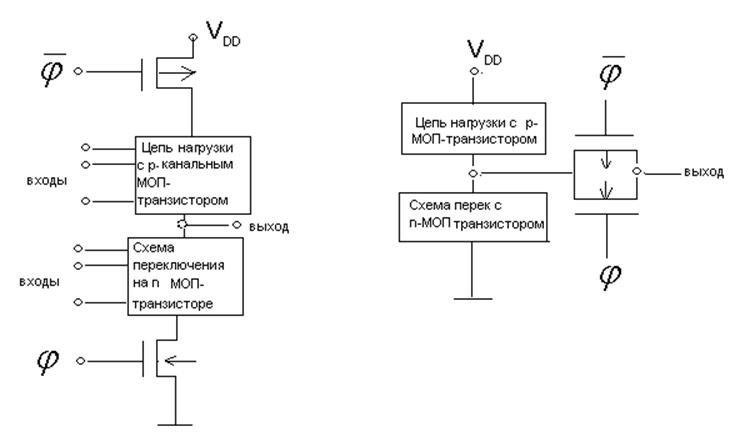

Вентиль И-НЕ, ИЛИ-НЕ. Схемы двух входовых вентилей И-НЕ представлены на рис.

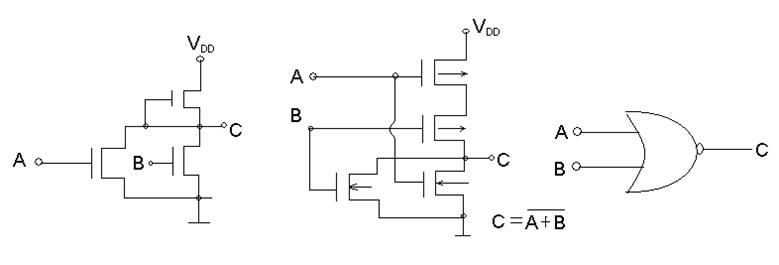

Схемы двухвходовых вентилей ИЛИ-НЕ представлены на рис.

На транзисторах, работающих в На КМОП – транзисторах Обозначение на схеме

режимах обогащения/обеднения

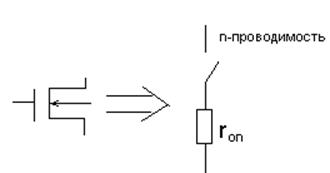

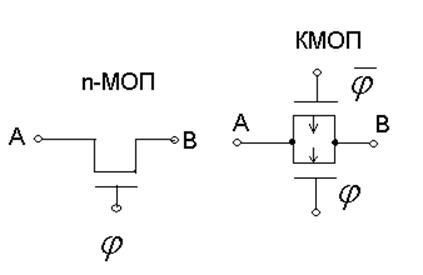

Ключевая модель. . Ключ, выполненный

Ключевая модель полевого транзистора

на ![]() канальном полевом МОП транзисторе, можно рассматривать как реле, замыкающее контакты при подаче на управляющий вход напряжения логической 1 ( в случае

канальном полевом МОП транзисторе, можно рассматривать как реле, замыкающее контакты при подаче на управляющий вход напряжения логической 1 ( в случае ![]() канального полевого МОП транзистора замыкание происходило бы при подаче на вход напряжения логического 0). Последовательное сопротивление

канального полевого МОП транзистора замыкание происходило бы при подаче на вход напряжения логического 0). Последовательное сопротивление ![]() — это сопротивление открытого полевого МОП транзистора.

— это сопротивление открытого полевого МОП транзистора.

— при малых значениях

— при малых значениях ![]() . Величина

. Величина ![]() пропорциональна

пропорциональна ![]() . Поэтому, нередко, на схеме вместо величины

. Поэтому, нередко, на схеме вместо величины ![]() указывают отношение

указывают отношение ![]() .

.

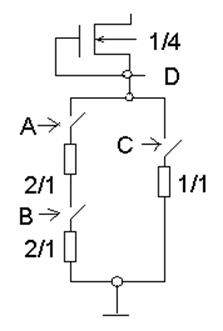

На рис. с помощью ключевой модели представлен вентиль, реализующий логическую функцию  .

.

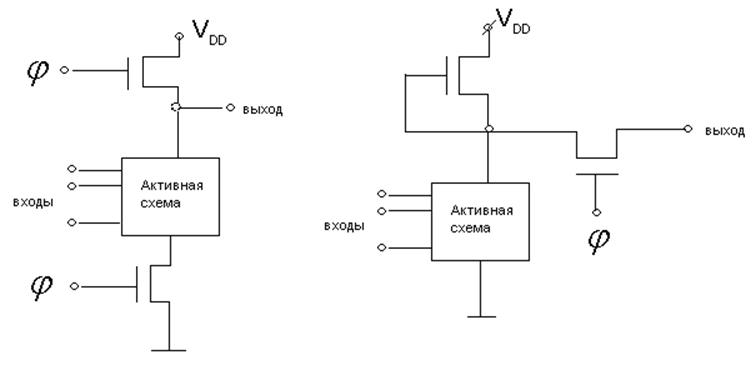

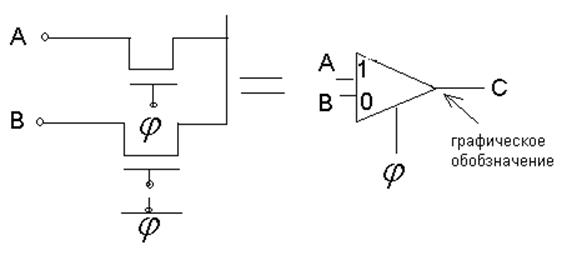

Вентили с тремя состояниями . Схемы вентилей с тремя состояниями в общем виде представлены на рис.

а ) б )

а ) б )

Управляющие вентили

а ) б )

На рис. представлена схема 2-1 – мультиплексора-демультиплексора

Функциональные устройства на МОП-структурах.

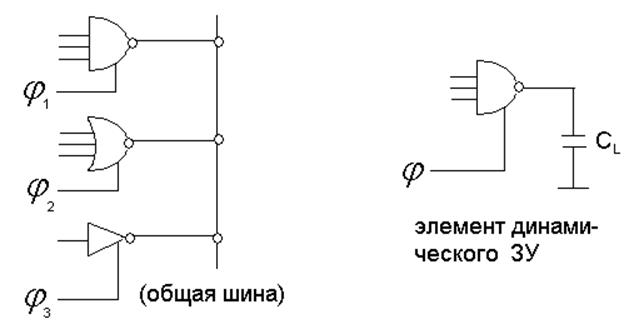

Регистры.

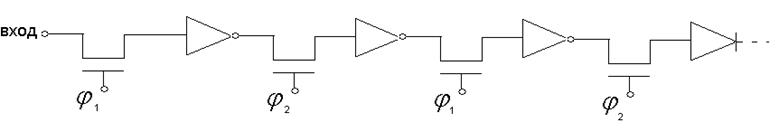

Базовая схема динамического регистра приведена на рис.

Последовательно соединив несколько регистров можно реализовать сдвиговый регистр (рис….)